Both tools include syntax highlighting. In the case of Altera Quartus editor, there is a very useful feature which is the possibility of entering templates for commonly used code blocks (entity, architecture, component) and also for design units (counters, registers, memories, etc.). Verilog Syntax Cheat Sheet. GitHub Gist: instantly share code, notes, and snippets. — The C Application Programming Interface (API) Committee (SV-CC) worked on errata and extensions to the Direct Programming Interface (DPI), the assertions and coverage APIs and the VPI features of System-Verilog 3.1. The committee chairs were: Vassilios Gerousis, SystemVerilog 3.1 and 3.1a Committee General Chair Basic/Design. Tidy Evaluation with rlang Cheatsheet. Tidy Evaluation (Tidy Eval) is a framework for doing non-standard evaluation in R that makes it easier to program with tidyverse functions. Non-standard evaluation, better thought of as “delayed evaluation,” lets you capture a user’s R code to run later in a new environment or against a new data frame.

For simple designs the major steps are:

- Compile the design

- Run the Simulation

- Generate Code Coverage Report

Compiling Verilog design using VCS

Included Options

- -cm coverage-type: specifies the type of coverage information to collect. The line, tgl, cond, fsm and path options enable statement (line), toggle, condition, FSM, and path coverage respectively. Any combination of coverage can be enabled simultaneously using the + sign e.g. -cm cond+line enables conditional and line coverage.

- -cm_line contassign: monitor continuous assignments for line coverage

- -cm_cond allops+anywidth+event: monitor non-logical operators, of any width, and always block sensitivity expressions for condition coverage

- -cm_noconst: try to automatically ignore constant expressions and unreachable statements

for line and condition coverage - +lint=all: turns on all verilog warnings

- +v2k: tells VCS to handle Verilog-2001 features, include this option if you are using those features

- -PP: turns on support for using the VPD trace output format

- -debug_all option allows to run the interactive DVE tool and use steps to debug the design

- -l file_name: logs the compiler messages to given file name

- -f file_name: tells VCS to read source files from the given file

Few optional arguments

- -sverilog: include this options if system verilog source files are also present. This enables compilation for system verilog source files.

- -v: use this flag to indicate which verilog files are part of the library and thus be compiled if needed.

- -timescale: can be used to specify how the abstract delay units in their design map into real time units e.g. -timescale=1ns/10ps

During compilation a subdirectory named csrc is created to store the files generated by compilation. This directory includes:

- Makefile for the compilation process

- Object files from the compilation. These object files are linked to create the simv executable.

- Intermediate C or Assembly source files.

Incremental Compilation

The source files are compiled on module-by-module basis. Incremental compilation means that if we run the vcs command again, only the modules that have changed after the last compilation are recompiled. VCS compares the modules in the source file to the descriptor information in the generated files from the last compilation, if a module’s contents are different from what VCS recorded in the last compilation, VCS recompiles the module.

Compile time options that affect incremental compilation all begin with -M.

Running the Simulation

For text based output use:

For debugging with DVE GUI use:

For Generating code coverage information run as:

Generating code coverage reports using VCS URG

For generating code coverage report in html form use the following command

To generate code coverage report in text form add the extra options as

A directory named urgReport will be created in current directory. This directory contains all the generated reports.

References

- VCS Quickstart

- VCS User Guide

FPGA

Flashing Guide

⚠️Modifying FPGA source may have unintended consequences⚠️

Device Compatibility

Overview

The FPGA handles:

- GPIO output

- Connections between board components

- Microphone processing (not provided in source code)

FPGA Source

FPGA source code is located here.

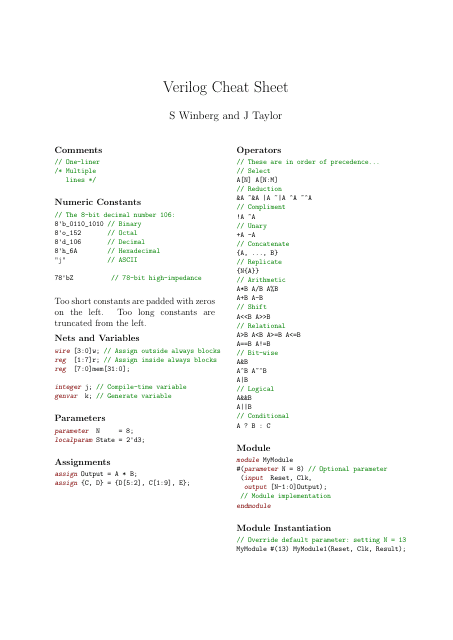

Verilog Cheat Sheet

For refreshers on FPGA Verilog HDL syntax and concepts, check out this cheat sheet.

FPGA Flashing

Below is a guide on how to flash a premade user-provided FPGA bitstream onto the Xilinx Spartan-6 FPGA for the MATRIX Voice.

We first need to install a few prerequisites.

Add the MATRIX repository and key.

Update your repository and packages.

Install the required packages.

Reboot your device.

Backup the stocksystem_voice.bit file.Copy your built system_voice.bit FPGA bitstream file to the blob folder.

Now you can flash the FPGA.

Reset the FPGA.

Flash the SPI Flash bootloader onto FPGA.

Verilog Syntax Cheat Sheet Pdf

You should receive the following (may vary due to user-provided file).

Flash the SPI Flash.

You should receive the following (may vary due to user-provided file).

Reset the FPGA.

In order to maintain compatibility with the matrixio-creator-init package, you'll need to backup the original voice.version file, and create your own.

Updating the matrixio-creator-init package will cause the stock FPGA bitstream to be flashed upon next boot.

You can stop sudo apt-get upgrade from automatically updating the matrixio-creator-init package with the following command.

Power off your device.

Wait until the green led on your Raspberry Pi blinks 10 times, then unplug the power cable from your Raspberry Pi.

Plug the power cable back into your Raspberry Pi.

Restore Original Firmware

To restore the original firmware, restore the stock system_voice.bit file in the blob folder.

Now you can flash the FPGA.

Reset the FPGA.

Flash the SPI Flash bootloader onto FPGA.

You should receive the following.

Flash the SPI Flash.

You should receive the following.

Reset the FPGA.

Restore the stock voice.version file.

Allow sudo apt-get upgrade to update the matrixio-creator-init package.

Verilog Syntax Cheat Sheet Examples

Power off your device.

Wait until the green led on your Raspberry Pi blinks 10 times, then unplug the power cable from your Raspberry Pi.

Verilog Code Example

Plug the power cable back into your Raspberry Pi.

System Verilog Syntax

Contents