A VHDL one-dimensional array of character enumeration can be forced as a sequence of character literals or as a based number with a radix of 2, 8, 10 or 16. For example, the following values are equivalent for a signal of type bitvector (0 to 3): Specifies the time to which the value is to be applied. The time is relative to the current. Subscribe to electronics-Tutorial email list and get Cheat Sheets, latest updates, tips & tricks about electronics- to your inbox. VHDL Cheat Sheet – Combinational Logic Author: Bryce Last modified by: Bryce Created Date: 5/26/2005 4:18:00 AM Company: None Other titles: VHDL Cheat Sheet. ES 4 VHDL reference sheet r.2019.02.19- This is a comment /. Multi-line comment (VHDL 2008 only)./ library IEEE; use IEEE.stdlogic1164. Use tounsigned for unsigned constants before VHDL 2008. Process blocks Reporting stu Writing to les (or stdout) for INDEXVAR in MIN to MAX loop- loop body here end loop; Sequential logic.

VHDL concepts, you should be able to quickly and e ciently create useful VHDL code. In this way, you will see VHDL as a valuable design, simulation and test tool. With the accompanying set of syntax and usage rules. But, as opposed to higher-level computer languages, VHDL is primarily used to describe hardware. The tendency for.

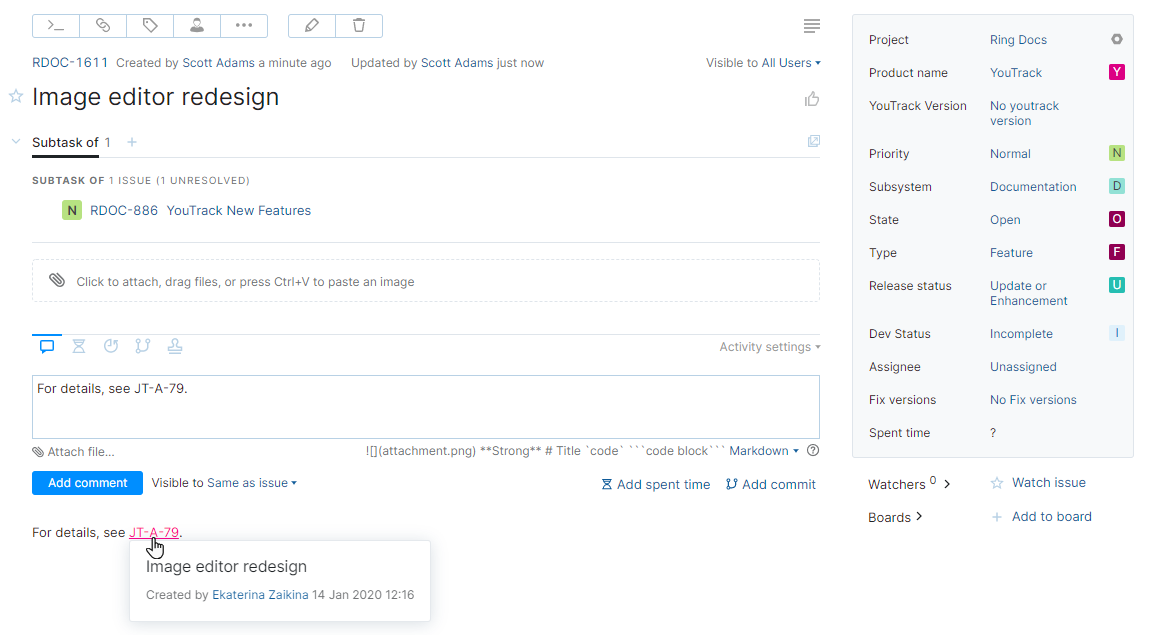

A test bench is required to verify the functionality of complex modules in VHDL. This posts contain information about how to write testbenches to get you started right away.

Common Constructs for a test bench

wait statement

The wait statement can take many forms but the most useful one in this context is

An example is:

This is used while testing combinational logic to give time to the simulator to calculate the output values based on the input signal values.

assert and report statements

The syntax for the assert statement is as follows:

The assert statement tests the boolean condition, if the condition is false, it outputs a message containing the message string to the simulator screen.

The severity level can be note, warning, error, or failure. The level failure normally aborts the simulation.

The report statement accepts a message string enclosed between double quotation marks as follows:

the severity argument can also be used in the statement.

The message after the report keyword can be concatenation of various messages separated by an & sign as follows:

If we want to display the signal values we can do so using the image function provided by the VHDL library. This function converts the value to a string representation, it is important to note that the data type in the report statement must be same as the data type of the variable. Also note that the image function is available for std_logic, integer etc data types but not for std_logic_vector, so for std_logic_vector we must perform type conversion. The following example demonstrates the statements:

Component Declaration

Under the architecture section (between architecture and begin), we must include a declaration for the module we are trying to test (instantiate). This is called a component declaration. For instantiating modules, all we need is the interface definition so that the VHDL can bind the module definition and definition. Note that the component declaration is exact replica of the entity declaration for the corresponding module. An example is as follows:

Component Instantiation

Under the begin statement in the architecture section, we instantiate the module as follows

Clock Generation

Clock is declared as a signal and we can declare the clock period as a constant. The clock can be generated using a separate process as follows:

Generating Stimulus

The stimulus to the UUT (Unit Under Test) can be generated either in a process or using the concurrent signal assignment statements.

Concurrent Assignment

The method using the concurrent assignment can be used to test combinational logic, an example is as follows:

process for generating stimulus

The above method of concurrent assignment is suitable for testing

small combinational logic, but a better alternative is to use the

VHDL process. The syntax of process could be something like:

The advantage of this approach is that we can use all type of control flow and decision statements like the loops, if statements etc.

A simple test bench for a 4 bit adder which takes two 4-bit vectors as input and generates a 4 bit sum is as follows:

The above example shows how all of the constructs shown above are used together to write a test bench.

Sometimes, there is more than one way to do something in VHDL. OK, most of the time, you can do things in many ways in VHDL. Let’s look at the situation where you want to assign different values to a signal, based on the value of another signal.

With / Select

Vhdl Example

The most specific way to do this is with as selected signal assignment. Based on several possible values of a, you assign a value to b. No redundancy in the code here. The official name for this VHDL with/select assignment is the selected signal assignment.

When / Else Assignment

The construct of a conditional signal assignment is a little more general. For each option, you have to give a condition. This means that you could write any boolean expression as a condition, which give you more freedom than equality checking. While this construct would give you more freedom, there is a bit more redundancy too. We had to write the equality check (a =) on every line. If you use a signal with a long name, this will make your code bulkier. Also, the separator that’s used in the selected signal assignment was a comma. In the conditional signal assignment, you need the else keyword. More code for the same functionality. Official name for this VHDL when/else assignment is the conditional signal assignment

Combinational Process with Case Statement

Vhdl Syntax Cheat Sheet Printable

The most generally usable construct is a process. Inside this process, you can write a case statement, or a cascade of if statements. There is even more redundancy here. You the skeleton code for a process (begin, end) and the sensitivity list. That’s not a big effort, but while I was drafting this, I had put b in the sensitivity list instead of a. Easy to make a small misstake. You also need to specify what happens in the other cases. Of course, you could do the same thing with a bunch of IF-statements, either consecutive or nested, but a case statement looks so much nicer.

While this last code snippet is the largest and perhaps most error-prone, it is probably also the most common. It uses two familiar and often-used constructs: the process and the case statements.

Hard to remember

The problem with the selected and conditional signal assignments is that there is no logic in their syntax. The meaning is almost identical, but the syntax is just different enough to throw you off. I know many engineers who permanenty have a copy of the Doulos Golden Reference Guide to VHDL lying on their desks. Which is good for Doulos, because their name gets mentioned all the time. But most people just memorize one way of getting the job done and stick with it.

Vhdl Syntax Guide

Please enable JavaScript to view the comments powered by Disqus.comments powered byVhdl Tutorial

Disqus